# HARDWARE IMPLEMENTATION OF NOC TOPOLOGIES

**Project Reference No.:** 47S\_Mtech\_0110

College : Reva University, Bengaluru

**Branch**: Department of Electronics and Computer Engineering

Guide(s) : Dr. Sanju V.

Student(S): Mr. Churanta Mondal

Ms. Chandana C. Savalgimath

Mr. Siddarth Sangavi

# **Keywords:**

Network-on-Chip (NoC), Topology optimization, Mesh, Torus, RiCoBiT, On-chip communication, Simulation environments, Resource constraints, Implementation hurdles, Chip designs, Compatibility issues, Integration complexities, Chip architectures

#### Introduction:

Modern chip designs face myriad challenges: increasing complexity, demand for higher performance in smaller sizes, and lower power consumption. Conventional bus-based interconnections, once fundamental, now hinder progress due to scalability constraints, high energy usage, and slow data transfer speeds. Enter Network-on-Chip (NoC), offering scalability, increased communication speed, reduced power consumption, flexibility, and improved error handling. NoC functions like an advanced road system within chips, facilitating seamless data exchange and enhancing overall chip performance. This paper explores NoC's effectiveness compared to traditional methods, highlighting its transformative potential in addressing modern chip design needs and advancing semiconductor technology.

NoC's scalability is vital in meeting the growing demand for integrated circuits with more power and features. It enables dynamic scaling without compromising efficiency or performance, unlike traditional bus-based systems. NoC significantly boosts communication speed between chip components, crucial for real-time processing and high-bandwidth data streaming. Additionally, NoC reduces energy consumption, enhancing power efficiency and battery life, crucial in energy-conscious computing. Its versatility allows for flexible chip layouts and integration of heterogeneous components, fostering creativity and tailored solutions for diverse application requirements.

NoCs offer unmatched scalability, performance, power efficiency, flexibility, and durability compared to conventional methods, marking a revolutionary milestone in chip design. Embracing NoC architectures enables chip designers to innovate beyond the constraints of traditional systems, shaping the future of computing towards faster, more energy-efficient, and highly integrated processors.

## **Objectives:**

In the realm of modern chip design, the imperative for efficient communication solutions has become increasingly pressing. Traditional bus-based systems, once stalwarts of chip architecture, are now beset by limitations in scalability, energy consumption, and speed. In response to these challenges, Network on-Chip (NoC) emerges as a compelling alternative, revolutionizing intra-chip communication by integrating a packet-switched network of routers and switches directly within the chip architecture. NoC offers a comprehensive array of advantages, including scalability to accommodate growing complexities, modularity for easier integration and maintenance, high performance to meet demanding computational requirements. flexibility to adapt to diverse chip architectures and applications, and energy efficiency to minimize power consumption. The presentation under scrutiny delves into the intricacies of NoC design, delving into various topologies such as mesh, torus, and RiCoBiT, to comprehensively assess their effectiveness within integrated circuits (ICs) and system-on-chips (SoCs). Through this exploration, the presentation aims to elucidate the transformative potential of NoC in overcoming the limitations of traditional bus-based systems, ushering in a new era of enhanced communication efficiency and optimized chip performance across a myriad of applications and industries. The current chip design landscape is changing quickly, making it more important than ever to find effective communication methods. Once the cornerstones of chip architecture, traditional bus-based systems now face severe restrictions in terms of performance, energy consumption, and scalability. As a result, Network-on-Chip (NoC) presents itself as a ground-breaking substitute that radically alters intrachip communication by integrating a packet-switched network of switches and routers into the chip's design. NoC offers many benefits, including high performance to meet demanding computational demands, flexibility to adapt to various architectures, scalability to accommodate growing complexity, modularity for seamless integration and maintenance, and energy efficiency to reduce power consumption. This talk goes into great detail about the nuances of NoC design, carefully looking at several topologies including mesh, torus, and RiCoBiT. This in-depth investigation seeks to evaluate them in integrated circuits (ICs) and system-on-chips (SoCs) in a comprehensive manner. By means of this careful examination, the talk aims to illuminate NoC's revolutionary potential by demonstrating its capacity to surpass the constraints of conventional bus-based systems. In the conclusion, this project aims to bring in a new era of improved communication effectiveness and optimized chip performance, meeting the various demands of various industries and applications in the dynamic semiconductor market.

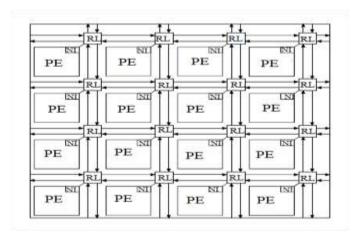

Fig: NOC Architecture

#### Methodology:

Mesh Topology Overview: Mesh topology, a common structure in WANs and peer-to-peer networks, establishes direct connections between every node and all others. This robust connectivity ensures each node's direct link to every other, enhancing network robustness and fault tolerance by enabling multiple communication paths. Redundancy within mesh topologies allows communication to persist through alternative paths if one fails, bolstering fault tolerance. Additionally, mesh topologies support easy network expansion, making them highly scalable. Their design facilitates simultaneous data transmission through different paths, efficiently managing network traffic. However, as the number of nodes increases, implementing mesh topologies becomes more complex and costly due to concerns regarding the exponential growth of connections. Mesh topology, a common architecture in peer-to-peer and wide area networks, creates connections directly between each node and all other nodes. Because many communication pathways are made possible by this robust connection, which guarantees that every node has a direct link to every other, the network's resilience and fault tolerance are improved. Fault tolerance is increased by the redundancy that mesh topologies provide, which enables communication to continue via backup pathways in the event that one fails. Furthermore, mesh topologies are very scalable since they provide simple network extension. Their design efficiently manages network traffic by enabling simultaneous data transmission over several pathways. However, because of worries about the exponential growth of connections, mesh topologies become increasingly difficult and expensive to design as the number of nodes rises.

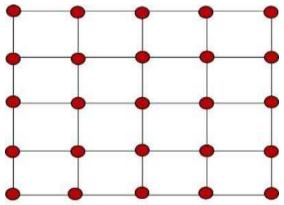

#### Fig: Mesh Topology

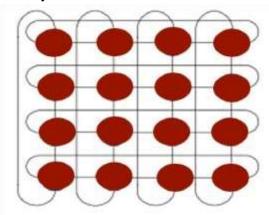

Torus Architecture Overview: Torus architecture, an extension of the mesh structure, forms a toroidal shape, thereby increasing connections and paths by wrapping the network around itself. This configuration enhances fault tolerance and reduces congestion within the network, making it highly scalable for both short and long-distance communication. Despite wiring complexity increasing with the number of dimensions in the torus and the intricacy involved with additional layers, torus topologies remain valuable for handling high communication demands and providing redundancy across a wide range of applications. Extending the mesh structure into a toroidal shape, torus architecture enhances connections and routes by encircling the network in a circle. This arrangement makes the network more resilient to faults and reduces congestion, making it extremely scalable for both short- and long-distance transmission. Torus topologies are still useful for handling high communication needs and providing redundancy across a wide range of applications, even if the wiring complexity increases with the number of dimensions in the torus and the complexity associated with additional layers.

Fig: Torus Topology

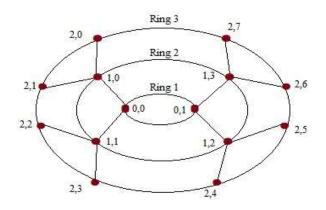

RiCoBiT Overview: RiCoBiT, short for Ring Connected Binary Tree, is utilized in Network-on-Chip (NoC) systems, combining the strengths of ring and binary tree topologies. In RiCoBiT, nodes form a binary tree with the root node connecting to all others, while nodes are grouped into rings, each containing two nodes. These rings are then connected hierarchically. This hierarchical setup facilitates efficient routing of data packets, resulting in a low maximum hop count for quick data packet travel between nodes and a low average hop count, thereby reducing distances between any two nodes. Consequently, RiCoBiT offers improved NoC system performance due to its efficient routing and low hop counts. Ring Connected Binary Tree, or RiCoBiT, combines the advantages of binary tree and ring topologies and is used in Network-on-Chip (NoC) systems. Nodes in RiCoBiT are arranged into rings, each with two nodes, and create a binary tree with the root node connecting to every other node. After that, these rings are connected hierarchically. This hierarchical configuration makes data packet routing more effective, resulting in a low average hop count that reduces the distance between any two nodes and a low maximum hop count that allows for quick data packet travel between nodes. As a result, RiCoBiT provides improved NoC system performance because of its effective routing and minimal hop count.

Fig: RiCoBiT Topology

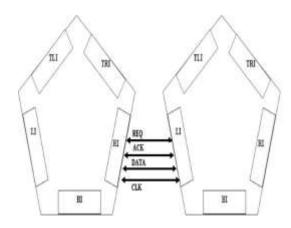

Fig: Interfacing Of Two Communicating RiCoBiT Nodes

### **Conclusion:**

Our review and comparative analysis of Network-on-Chip (NoC) topologies offer valuable insights into their characteristics, advantages, and trade-offs. Mesh and Torus architectures excel in scalability and low latency for short-distance communication, while Tree architectures provide hierarchical organization and fault tolerance, and Binary Tree architectures offer higher bandwidth. These findings underscore the importance of selecting the appropriate NoC topology based on specific application requirements and design constraints.

The primary focus of our project is to optimize mesh, torus, and RiCoBiT Network-on-Chip (NoC) topologies tailored for on-chip communication. With clear objectives in mind, we aim to enhance their performance and scalability, particularly under heavy workloads where efficiency is paramount. Our efforts will center on improving data exchange mechanisms and reducing latency to ensure smoother and more efficient operation of the overall system. Through these optimizations, we anticipate that the optimized NoC topologies will emerge as leading solutions, offering unparalleled performance, scalability, and reliability, ultimately ushering in a new era of more efficient integrated circuits.

Our study provides crucial understandings of NoC topologies' features, benefits, and drawbacks. Mesh and Torus architectures prioritize minimal latency and outstanding scalability, while Binary Tree topologies offer better bandwidth, and Tree architectures ensure fault tolerance and hierarchical organization. By comprehending the advantages and disadvantages of each topology, designers can make informed choices to maximize efficiency and performance in communication and chip design. Overall, our project aims to optimize NoC topologies for enhanced performance and scalability, potentially revolutionizing various applications and industries.

## Scope for future work:

Future work could explore additional NoC topologies beyond mesh, torus, and RiCoBiT, broadening the scope of potential solutions for on-chip communication. Incorporating emerging technologies such as machine learning, quantum computing, or photonic interconnects could further enhance the performance and capabilities of NoC architectures. Real-world validation and testing of optimized NoC topologies on actual chip prototypes or production chips would provide valuable insights into their practical effectiveness. Developing mechanisms for NoC topologies to dynamically adapt to changing workload conditions or chip configurations could improve their flexibility and efficiency. Furthermore, future enhancements could focus on further reducing power consumption in NoC designs through techniques such as dynamic voltage and frequency scaling or energy-aware routing algorithms. The main goal of the research is to optimize the mesh, torus, and RiCoBiT NoC (Network-on-Chip) topologies for on-chip communication, which is an essential component of contemporary chip architecture. But in aiming for greatness in these particular areas, the initiative may unintentionally ignore other, equally viable options. Even though the team wants to create realistic simulation scenarios, it can be difficult to fully replicate workloads and chip conditions found in the actual world. The project also has to deal with resource constraints, such as limited time, labour, and computing resources. The extent and depth of optimization and testing that can be conducted within the project's timetable may be limited by these limitations. Furthermore, there could be implementation roadblocks, such compatibility problems and integration complexity, that prevent a smooth transition from efficient NoC topologies in simulation to realworld semiconductor designs. It's also critical to acknowledge that the project's conclusions and optimizations might be rather specific, linked to specific chip architectures or application scenarios. As a result, even while the conclusions drawn are extremely valuable within the parameters they were given, there may be some limitations to their applicability in larger settings. Achieving a balance between these factors will be essential to guaranteeing that the project's results provide significant progress while recognizing the complexities and constraints specific to its field.